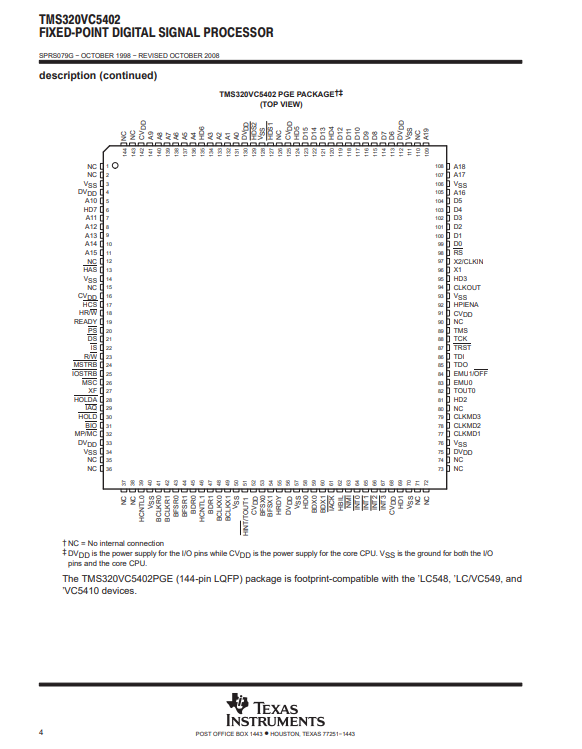

TMS320VC5402PGE100 IC DIG SIG PROCESADOR 144-LQFP

Parámetro del producto

Descripción

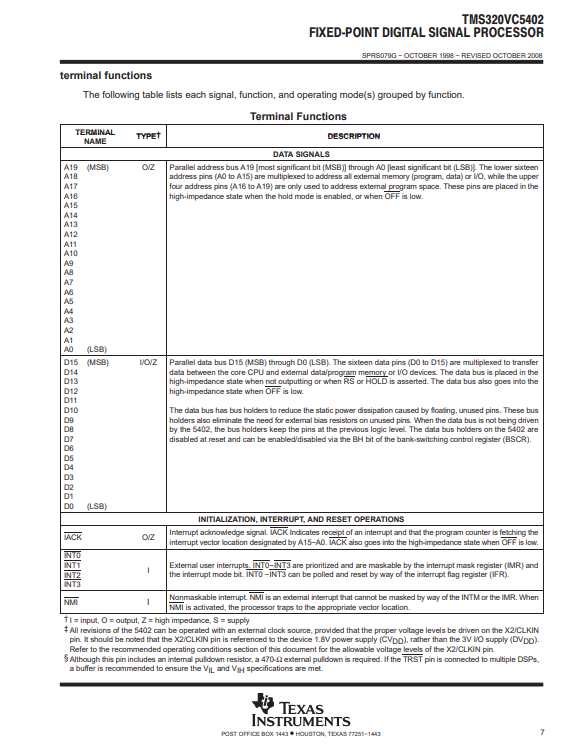

El procesador de señal digital (DSP) de punto fijo TMS320VC5402 (en lo sucesivo denominado 5402 a menos que se especifique lo contrario) se basa en una arquitectura Harvard modificada avanzada que tiene un bus de memoria de programa y tres buses de memoria de datos.Este procesador proporciona una unidad lógica aritmética (ALU) con un alto grado de paralelismo, lógica de hardware específica de la aplicación, memoria en chip y periféricos en chip adicionales.La base de la flexibilidad operativa y la velocidad de este DSP es un conjunto de instrucciones altamente especializado.Los espacios de datos y programas separados permiten el acceso simultáneo a las instrucciones y datos del programa, proporcionando un alto grado de paralelismo.Se pueden realizar dos operaciones de lectura y una operación de escritura en un solo ciclo.Las instrucciones con almacenamiento paralelo y las instrucciones específicas de la aplicación pueden utilizar completamente esta arquitectura.Además, los datos se pueden transferir entre datos y espacios de programa.Dicho paralelismo admite un poderoso conjunto de operaciones aritméticas, lógicas y de manipulación de bits que se pueden realizar en un solo ciclo de máquina.Además, el 5402 incluye los mecanismos de control para gestionar interrupciones, operaciones repetidas y llamadas de función.

| Especificaciones: | |

| Atributo | Valor |

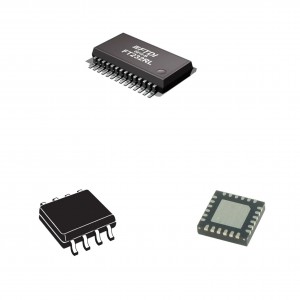

| Categoría | Circuitos Integrados (CI) |

| Embebido - DSP (procesadores de señal digital) | |

| Fabricante | Instrumentos Texas |

| Serie | TMS320C54x |

| Paquete | Bandeja |

| Estado de la pieza | Activo |

| Tipo | Punto fijo |

| Interfaz | Interfaz de host, McBSP |

| Velocidad de reloj | 100 MHz |

| Memoria no volátil | ROM (8kB) |

| RAM en chip | 32kB |

| Voltaje - E/S | 3,30 V |

| Voltaje - Núcleo | 1,80 V |

| Temperatura de funcionamiento | -40°C ~ 100°C (TC) |

| Tipo de montaje | Montaje superficial |

| Paquete / Caja | 144-LQFP |

| Paquete de dispositivo del proveedor | 144-LQFP (20x20) |

| Número de producto básico | TMS320 |

RelacionadoPRODUCTOS

-

Teléfono

-

Correo electrónico

-

skype

-

whatsapp

whatsapp