TMS320C6657CZHA IC DSP FIJO/PUNTO FLOTANTE 625FCBGA

Parámetro del producto

Descripción

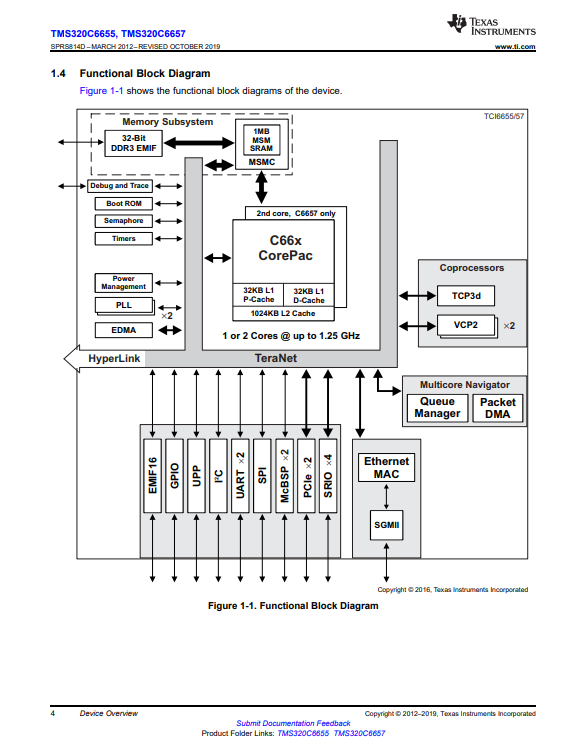

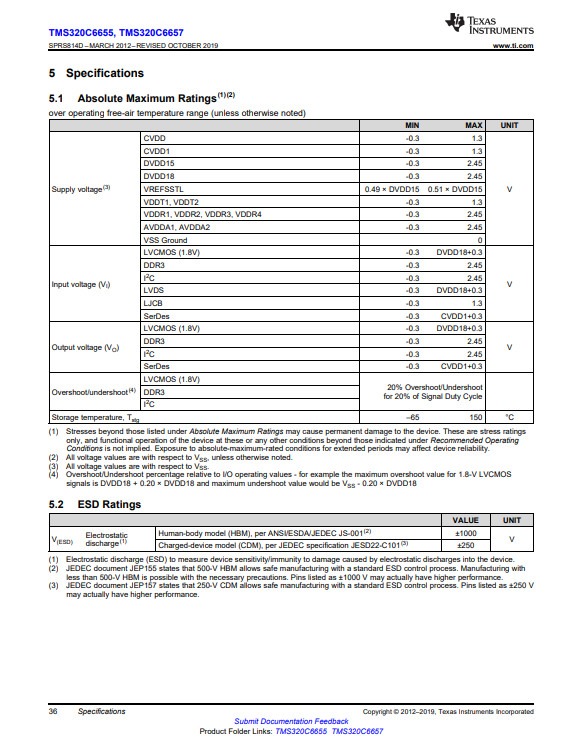

La arquitectura KeyStone de TI proporciona una plataforma programable que integra varios subsistemas (núcleos C66x, subsistema de memoria, periféricos y aceleradores) y utiliza varios componentes y técnicas innovadores para maximizar la comunicación dentro del dispositivo y entre dispositivos que permite que los diversos recursos DSP funcionen de manera eficiente y sin problemas.El centro de esta arquitectura son los componentes clave, como Multicore Navigator, que permite una gestión de datos eficiente entre los diversos componentes del dispositivo.TeraNet es una estructura de conmutación sin bloqueo que permite un movimiento de datos interno rápido y sin conflictos.El controlador de memoria compartida multinúcleo permite el acceso a la memoria externa y compartida directamente sin utilizar la capacidad de la estructura del conmutador.Para uso de punto fijo, el núcleo C66x tiene 4 veces la capacidad de acumulación múltiple (MAC) de los núcleos C64x+.Además, el núcleo C66x integra la capacidad de punto flotante y el rendimiento computacional sin procesar por núcleo es líder en la industria de 40 GMACS por núcleo y 20 GFLOPS por núcleo (frecuencia operativa de 1,25 GHz).El núcleo C66x puede ejecutar 8 operaciones MAC de punto flotante de precisión simple por ciclo y puede realizar operaciones de precisión doble y mixta y cumple con IEEE 754.El núcleo C66x incorpora 90 instrucciones nuevas (en comparación con el núcleo C64x+) destinadas al procesamiento orientado a matemáticas vectoriales y de coma flotante.Estas mejoras generan mejoras de rendimiento considerables en los núcleos DSP populares utilizados en el procesamiento de señales, funciones matemáticas y de adquisición de imágenes.El núcleo C66x es compatible con códigos anteriores con los núcleos DSP de punto flotante y fijo C6000 de la generación anterior de TI, lo que garantiza la portabilidad del software y ciclos de desarrollo de software más cortos para las aplicaciones que migran a un hardware más rápido.El C665x DSP integra una gran cantidad de memoria en chip.Además de los 32 KB de caché de datos y programas L1, se pueden configurar 1024 KB de memoria dedicada como memoria RAM asignada o caché.El dispositivo también integra 1024 KB de memoria compartida multinúcleo que se puede utilizar como SRAM L2 compartida y/o SRAM L3 compartida.Todas las memorias L2 incorporan detección y corrección de errores.Para un acceso rápido a la memoria externa, este dispositivo incluye una interfaz de memoria externa (EMIF) DDR-3 de 32 bits que funciona a una velocidad de 1333 MHz y es compatible con ECC DRAM.

| Especificaciones: | |

| Atributo | Valor |

| Categoría | Circuitos Integrados (CI) |

| Embebido - DSP (procesadores de señal digital) | |

| Fabricante | Instrumentos Texas |

| Serie | TMS320C66x |

| Paquete | Bandeja |

| Estado de la pieza | Activo |

| Tipo | Punto fijo/flotante |

| Interfaz | DDR3, EBI/EMI, Ethernet, McBSP, PCIe, I²C, SPI, UART, UPP |

| Velocidad de reloj | 1GHz |

| Memoria no volátil | ROM (128kB) |

| RAM en chip | 2,06 MB |

| Voltaje - E/S | 1,0 V, 1,5 V, 1,8 V |

| Voltaje - Núcleo | 1,00 V |

| Temperatura de funcionamiento | -40°C ~ 100°C (TC) |

| Tipo de montaje | Montaje superficial |

| Paquete / Caja | 625-BFBGA, FCBGA |

| Paquete de dispositivo del proveedor | 625-FCBGA (21x21) |

| Número de producto básico | TMS320 |

RelacionadoPRODUCTOS

-

Teléfono

-

Correo electrónico

-

skype

-

whatsapp

whatsapp