EP1C6Q240C8N CI FPGA 185 E/S 240QFP

Parámetro del producto

Descripción

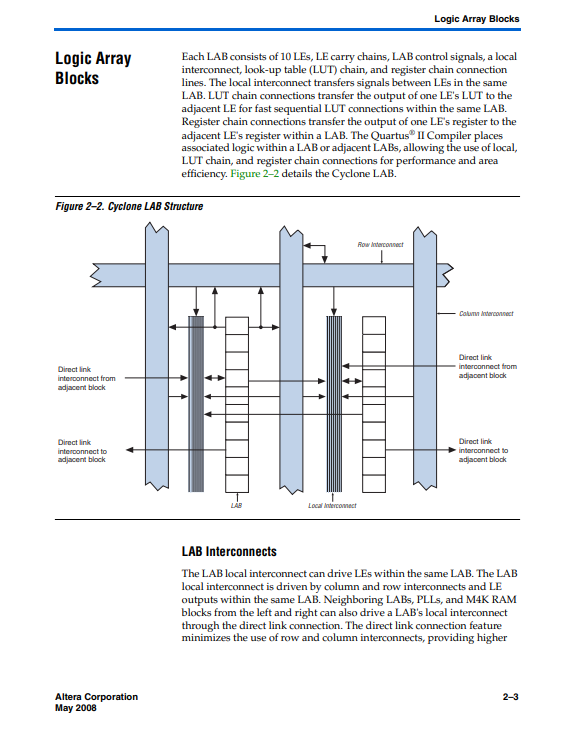

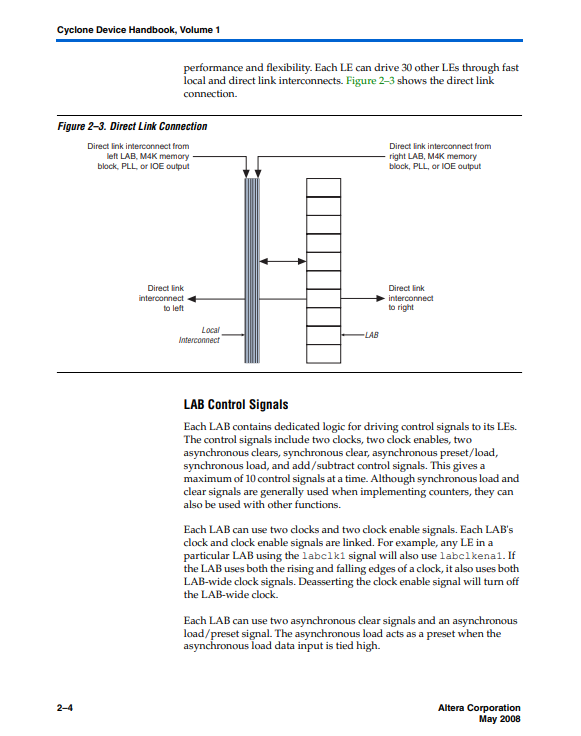

Los dispositivos Cyclone® contienen una arquitectura bidimensional basada en filas y columnas para implementar una lógica personalizada.Las interconexiones de columna y fila de diferentes velocidades proporcionan interconexiones de señal entre los LAB y los bloques de memoria integrados.La matriz lógica consta de LAB, con 10 LE en cada LAB.Un LE es una pequeña unidad de lógica que proporciona una implementación eficiente de las funciones lógicas del usuario.Los laboratorios se agrupan en filas y columnas en todo el dispositivo.Los dispositivos de ciclón oscilan entre 2910 y 20 060 LE.Los bloques de RAM M4K son verdaderos bloques de memoria de doble puerto con 4K bits de memoria más paridad (4608 bits).Estos bloques proporcionan memoria dedicada de puerto dual verdadero, puerto dual simple o puerto único de hasta 36 bits de ancho a hasta 250 MHz.Estos bloques se agrupan en columnas en todo el dispositivo entre ciertos LAB.Los dispositivos Cyclone ofrecen entre 60 y 288 Kbits de RAM integrada.Cada pin de E/S del dispositivo Cyclone es alimentado por un elemento de E/S (IOE) ubicado en los extremos de las filas y columnas de LAB alrededor de la periferia del dispositivo.Los pines de E/S admiten varios estándares de E/S diferenciales y de terminación única, como el estándar PCI de 66 y 33 MHz, 64 y 32 bits y el estándar de E/S LVDS de hasta 640 Mbps.Cada IOE contiene un búfer de E/S bidireccional y tres registros para registrar señales de entrada, salida y habilitación de salida.Los pines DQS, DQ y DM de doble propósito junto con las cadenas de retardo (usadas para alinear en fase las señales DDR) brindan soporte de interfaz con dispositivos de memoria externa como DDR SDRAM y dispositivos FCRAM a hasta 133 MHz (266 Mbps).Los dispositivos Cyclone proporcionan una red de reloj global y hasta dos PLL.La red de reloj global consta de ocho líneas de reloj global que recorren todo el dispositivo.La red de reloj global puede proporcionar relojes para todos los recursos dentro del dispositivo, como IOE, LE y bloques de memoria.Las líneas de reloj global también se pueden utilizar para señales de control.Los Cyclone PLL proporcionan reloj de uso general con multiplicación de reloj y cambio de fase, así como salidas externas para soporte de E/S diferencial de alta velocidad.

| Especificaciones: | |

| Atributo | Valor |

| Categoría | Circuitos Integrados (CI) |

| Integrado: FPGA (matriz de puertas programables en campo) | |

| Fabricante | Intel |

| Serie | Cyclone® |

| Paquete | Bandeja |

| Estado de la pieza | Obsoleto |

| Número de LAB/CLB | 598 |

| Número de elementos lógicos/celdas | 5980 |

| Bits de RAM totales | 92160 |

| Número de E/S | 185 |

| Suministro de voltaje | 1.425V ~ 1.575V |

| Tipo de montaje | Montaje superficial |

| Temperatura de funcionamiento | 0°C ~ 85°C (TJ) |

| Paquete / Caja | 240-BFQFP |

| Paquete de dispositivo del proveedor | 240-PQFP (32x32) |

| Número de producto básico | EP1C6 |

RelacionadoPRODUCTOS

-

Teléfono

-

Correo electrónico

-

skype

-

whatsapp

whatsapp